We are excited to announce the launch of new wafer bump plating process.

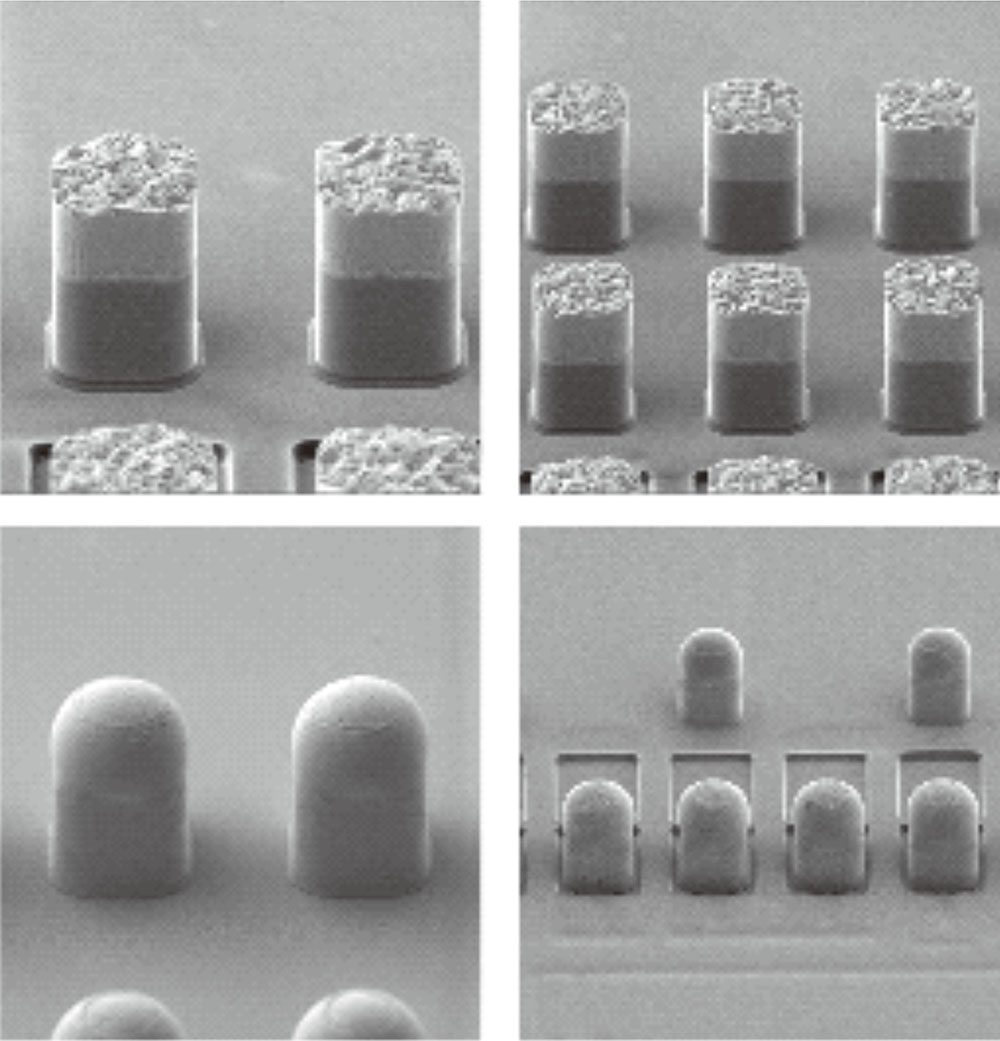

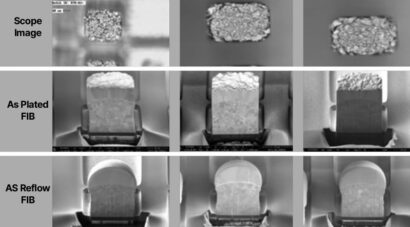

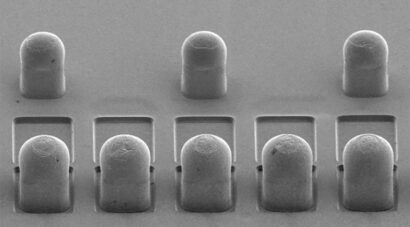

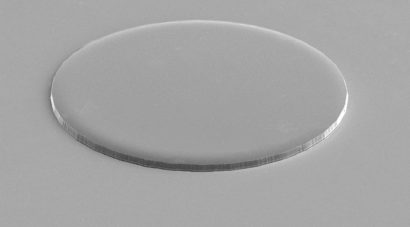

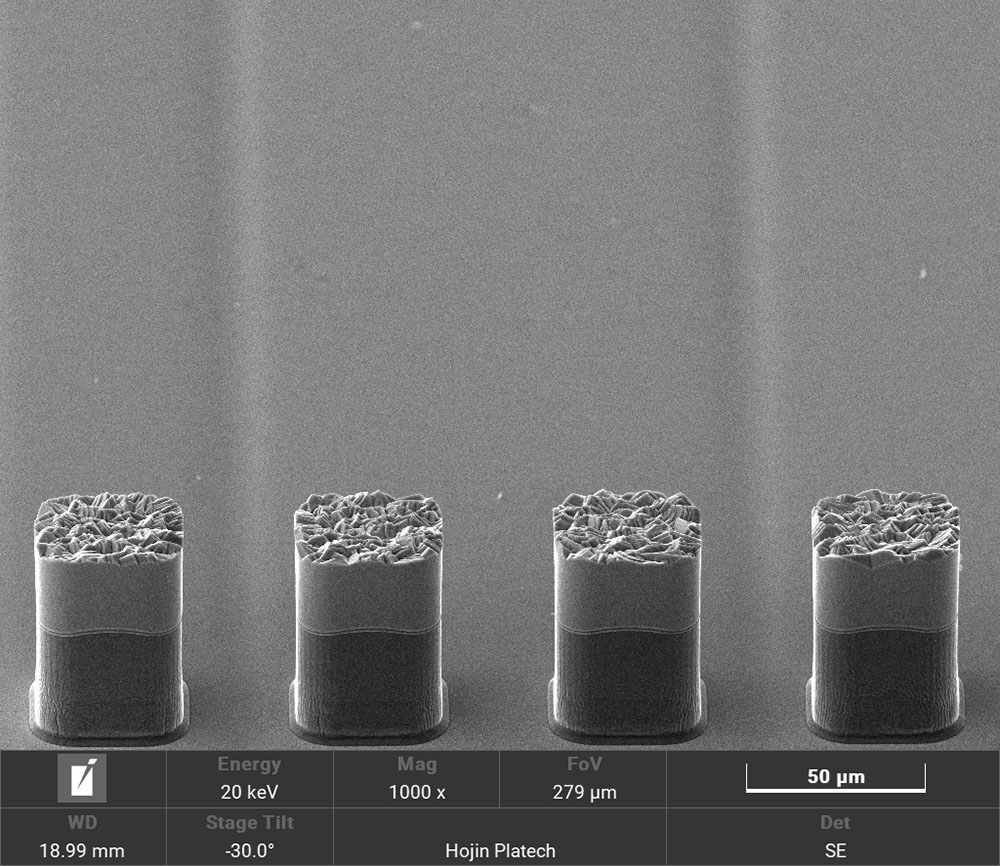

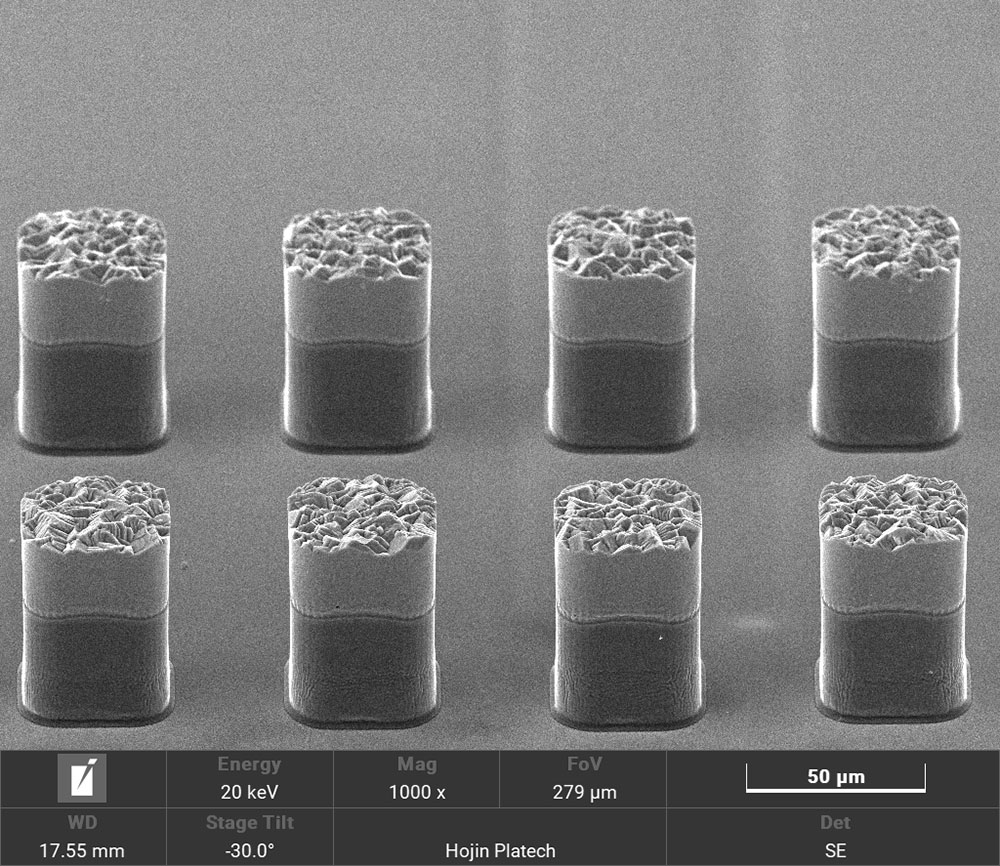

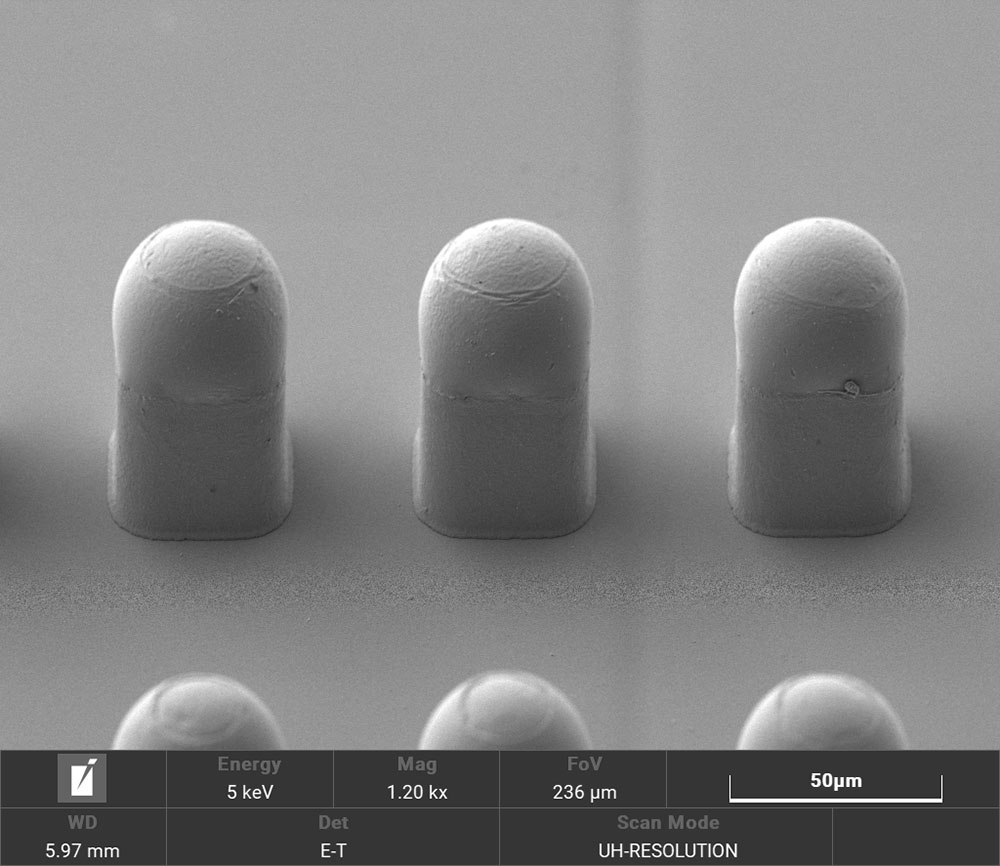

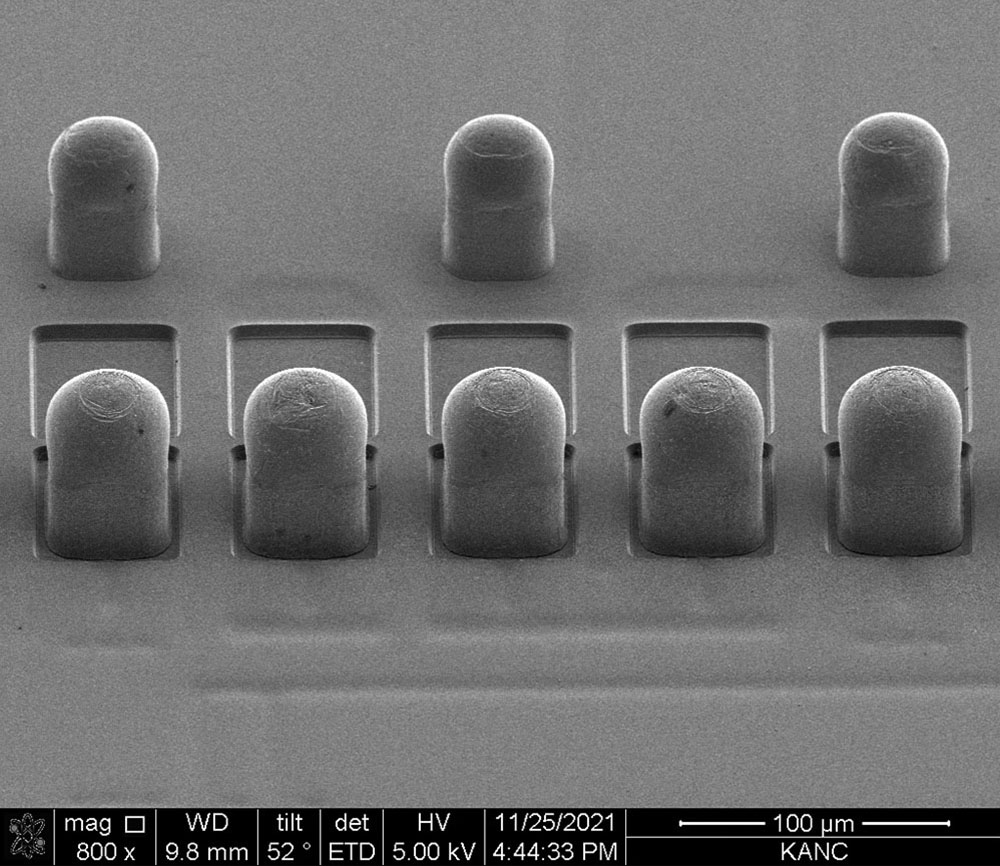

SupraSol WLT/WLS is designed for semiconductor wafer bump plating, utilizing pure materials with Low Alpha Tin levels below 0.002 cph/cm2. It is suitable for various plating processes such as C4, Cu pillar capping, and Micro bump, ensuring uniform thickness distribution (WID, WIW) and alloy ratio. Whether dealing with different bump diameters, pitch variations, complex and intricate patterns with significant differences, or the need for thickness consistency improvement after Cu pillar plating, it guarantees uniform thickness.

SupraSol WLT/WLT-M: Pure Tin Bump Plating process

SupraSol WLS: Tin-Silver Bump Plating process

We kindly ask for your continued interest and support.

Thank you.